### **General Description**

The MAX038 is a high-frequency, precision function generator producing accurate, high-frequency triangle, sawtooth, sine, square, and pulse waveforms with a minimum of external components. The output frequency can be controlled over a frequency range of 0.1Hz to 20MHz by an internal 2.5V bandgap voltage reference and an external resistor and capacitor. The duty cycle can be varied over a wide range by applying a ±2.3V control signal, facilitating pulse-width modulation and the generation of sawtooth waveforms. Frequency modulation and frequency sweeping are achieved in the same way. The duty cycle and frequency controls are independent.

Sine, square, or triangle waveforms can be selected at the output by setting the appropriate code at two TTL-compatible select pins. The output signal for all waveforms is a 2V<sub>P-P</sub> signal that is symmetrical around ground. The low-impedance output can drive up to ±20mA.

The TTL-compatible SYNC output from the internal oscillator maintains a 50% duty cycle—regardless of the duty cycle of the other waveforms—to synchronize other devices in the system. The internal oscillator can be synchronized to an external TTL clock connected to PDI.

#### **Features**

- ♦ 0.1Hz to 20MHz Operating Frequency Range

- ♦ Triangle, Sawtooth, Sine, Square, and Pulse **Waveforms**

- ♦ Independent Frequency and Duty-Cycle **Adjustments**

- ♦ 350 to 1 Frequency Sweep Range

- ♦ 15% to 85% Variable Duty Cycle

- ♦ Low-Impedance Output Buffer: 0.1Ω

- **♦ Low 200ppm/°C Temperature Drift**

### Ordering Information

| PART       | TEMP RANGE   | PIN-PACKAGE    |

|------------|--------------|----------------|

| MAX038CPP  | 0°C to +70°C | 20 Plastic DIP |

| MAX038CWP  | 0°C to +70°C | 20 SO          |

| MAX038C/D* | 0°C to +70°C | Dice           |

<sup>\*</sup> Contact factory prior to design.

### **Applications**

**Precision Function Generators**

Voltage-Controlled Oscillators

Frequency Modulators

Pulse-Width Modulators

Phase-Locked Loops

Frequency Synthesizer

FSK Generator—Sine and Square Waves

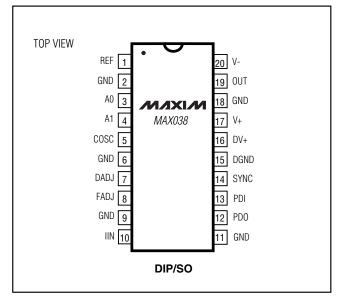

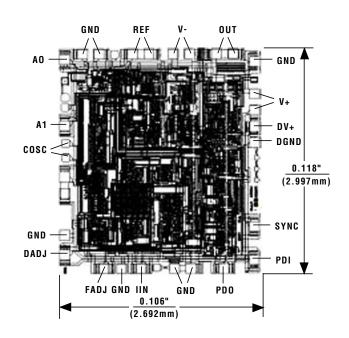

### **Pin Configuration**

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, GND =  $D_{GND}$  = 0V, V+ = DV+ = 5V, V- = -5V,  $V_{DADJ}$  =  $V_{FADJ}$  =  $V_{PDI}$  =  $V_{PDO}$  = 0V, CF = 100pF,  $R_{IN}$  = 25k $\Omega$  R<sub>L</sub> = 1k $\Omega$ , C<sub>L</sub> = 20pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                               | SYMBOL                               | CONDITIONS                                     | MIN  | TYP  | MAX   | UNITS            |

|-----------------------------------------|--------------------------------------|------------------------------------------------|------|------|-------|------------------|

| FREQUENCY CHARACTERISTIC                | cs                                   |                                                |      |      |       |                  |

| Maximum Operating Frequency             | Fo                                   | C <sub>F</sub> ≤ 15pF, I <sub>IN</sub> = 500µA | 20.0 | 40.0 |       | MHz              |

| Frequency Programming                   | I <sub>IN</sub>                      | V <sub>FADJ</sub> = 0V                         | 2.50 |      | 750   | μА               |

| Current                                 |                                      | VFADJ = -3V                                    | 1.25 |      | 375   |                  |

| IIN Offset Voltage                      | V <sub>IN</sub>                      |                                                |      | ±1.0 | ±2.0  | mV               |

| Frequency Temperature                   | ΔF <sub>O</sub> /°C                  | VFADJ = 0V                                     |      | 600  |       | ppm/°C           |

| Coefficient                             | F <sub>o</sub> /°C                   | $V_{FADJ} = -3V$                               |      | 200  |       |                  |

| Frequency Power-Supply<br>Rejection     | $\frac{(\Delta F_0/F_0)}{\Delta V+}$ | V- = -5V, V+ = 4.75V to 5.25V                  |      | ±0.4 | ±2.00 | - %/V            |

|                                         | $\frac{(\Delta F_0/F_0)}{\Delta V}$  | V+ = 5V, V- = -4.75V to -5.25V                 |      | ±0.2 | ±1.00 |                  |

| OUTPUT AMPLIFIER (applies to            | all waveforn                         | ns)                                            | •    |      |       |                  |

| Output Peak-to-Peak Symmetry            | Vout                                 |                                                |      | ±4   |       | mV               |

| Output Resistance                       | Rout                                 |                                                |      | 0.1  | 0.2   | Ω                |

| Output Short-Circuit Current            | lout                                 | Short circuit to GND                           |      | 40   |       | mA               |

| SQUARE-WAVE OUTPUT ( $R_L =$            | 100Ω)                                |                                                |      |      |       |                  |

| Amplitude                               | Vout                                 |                                                | 1.9  | 2.0  | 2.1   | V <sub>P-P</sub> |

| Rise Time                               | t <sub>R</sub>                       | 10% to 90%                                     |      | 12   |       | ns               |

| Fall Time                               | tF                                   | 90% to 10%                                     |      | 12   |       | ns               |

| Duty Cycle                              | dc                                   | $V_{DADJ} = 0V$ , $dc = t_{ON}/t \times 100\%$ | 47   | 50   | 53    | %                |

| TRIANGLE-WAVE OUTPUT (RL                | <b>= 100</b> Ω)                      |                                                |      |      |       |                  |

| Amplitude                               | Vout                                 |                                                | 1.9  | 2.0  | 2.1   | V <sub>P-P</sub> |

| Nonlinearity                            |                                      | $F_O = 100kHz$ , 5% to 95%                     |      | 0.5  |       | %                |

| Duty Cycle                              | dc                                   | V <sub>DADJ</sub> = 0V (Note 1)                | 47   | 50   | 53    | %                |

| SINE-WAVE OUTPUT (R <sub>L</sub> = 1009 | Ω)                                   |                                                |      |      | ·     |                  |

|                                         | Vout                                 |                                                | 1.9  | 2.0  | 2.1   | V <sub>P-P</sub> |

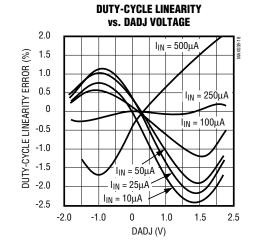

| Total Harmonic Distortion               | THD                                  | $C_F = 1000pF, F_O = 100kHz$                   |      | 2.0  |       | %                |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, GND = D<sub>GND</sub> = 0V, V+ = DV+ = 5V, V- = -5V, V<sub>DADJ</sub> = V<sub>FADJ</sub> = V<sub>PDI</sub> = V<sub>PDO</sub> = 0V, C<sub>F</sub> = 100pF,  $R_{IN} = 25k\Omega$   $R_{L} = 1k\Omega$ ,  $R_{L} = 1k\Omega$ , R

| PARAMETER                            | SYMBOL                             | CONDITIONS                                                            | MIN   | TYP  | MAX   | UNITS  |

|--------------------------------------|------------------------------------|-----------------------------------------------------------------------|-------|------|-------|--------|

| SYNC OUTPUT                          |                                    |                                                                       |       |      |       |        |

| Output Low Voltage                   | V <sub>OL</sub>                    | I <sub>SINK</sub> = 3.2mA                                             |       | 0.3  | 0.4   | V      |

| Output High Voltage                  | Voh                                | ISOURCE = 400µA                                                       | 2.8   | 3.5  |       | V      |

| Rise Time                            | t <sub>R</sub>                     | 10% to 90%, $R_L = 3k\Omega$ , $C_L = 15pF$                           |       | 10   |       | ns     |

| Fall Time                            | tF                                 | 90% to 10%, $R_L = 3k\Omega$ , $C_L = 15pF$                           |       | 10   |       | ns     |

| Duty Cycle                           | dcsync                             |                                                                       |       | 50   |       | %      |

| DUTY-CYCLE ADJUSTMENT (DA            | ADJ)                               |                                                                       |       |      |       |        |

| DADJ Input Current                   | IDADJ                              |                                                                       | 190   | 250  | 320   | μΑ     |

| DADJ Voltage Range                   | V <sub>DADJ</sub>                  |                                                                       |       | ±2.3 |       | V      |

| Duty-Cycle Adjustment Range          | dc                                 | -2.3V ≤ V <sub>DADJ</sub> ≤ +2.3V                                     | 15    |      | 85    | %      |

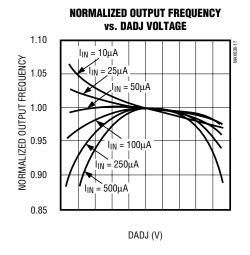

| DADJ Nonlinearity                    | dc/V <sub>FADJ</sub>               | -2V ≤ V <sub>DADJ</sub> ≤ +2V                                         |       | 2    | 4     | %      |

| Change in Output Frequency with DADJ | F <sub>o</sub> /V <sub>DADJ</sub>  | -2V ≤ V <sub>DADJ</sub> ≤ +2V                                         |       | ±2.5 | ±8    | %      |

| Maximum DADJ Modulating<br>Frequency | FDC                                |                                                                       |       | 2    |       | MHz    |

| FREQUENCY ADJUSTMENT (FA             | DJ)                                |                                                                       | •     |      |       | •      |

| FADJ Input Current                   | IFADJ                              |                                                                       | 190   | 250  | 320   | μΑ     |

| FADJ Voltage Range                   | VFADJ                              |                                                                       |       | ±2.4 |       | V      |

| Frequency Sweep Range                | Fo                                 | -2.4V ≤ V <sub>FADJ</sub> ≤ +2.4V                                     |       | ±70  |       | %      |

| FM Nonlinearity with FADJ            | F <sub>o</sub> /V <sub>FADJ</sub>  | -2V ≤ V <sub>FADJ</sub> ≤ +2V                                         |       | ±0.2 |       | %      |

| Change in Duty Cycle with FADJ       | dc/V <sub>FADJ</sub>               | -2V ≤ V <sub>FADJ</sub> ≤ +2V                                         |       | ±2   |       | %      |

| Maximum FADJ Modulating<br>Frequency | FF                                 |                                                                       |       | 2    |       | MHz    |

| VOLTAGE REFERENCE                    |                                    |                                                                       | •     |      |       | •      |

| Output Voltage                       | V <sub>REF</sub>                   | I <sub>REF</sub> = 0                                                  | 2.48  | 2.50 | 2.52  | V      |

| Temperature Coefficient              | V <sub>REF</sub> /°C               |                                                                       |       | 20   |       | ppm/°C |

|                                      | V <sub>REF</sub> /I <sub>REF</sub> | 0mA ≤ I <sub>REF</sub> ≤ 4mA (source)                                 |       | 1    | 2     | mV/mA  |

| Load Regulation                      |                                    | $-100\mu$ A $\leq$ I <sub>REF</sub> $\leq$ 0 $\mu$ A (sink)           |       | 1    | 4     |        |

| Line Regulation                      | V <sub>REF</sub> /V+               | $4.75V \le V + \le 5.25V \text{ (Note 2)}$                            |       | 1    | 2     | mV/V   |

| LOGIC INPUTS (A0, A1, PDI)           | · IILI/··                          |                                                                       |       |      |       | ,      |

| Input Low Voltage                    | VIL                                |                                                                       |       |      | 0.8   | V      |

| Input High Voltage                   | VIH                                |                                                                       | 2.4   |      |       | V      |

| Input Current (A0, A1)               | I <sub>IL</sub> , I <sub>IH</sub>  | V <sub>AO</sub> , V <sub>A1</sub> = V <sub>IL</sub> , V <sub>IH</sub> |       |      | ±5    | μA     |

| Input Current (PDI)                  | IIL, IIH                           | V <sub>PDI</sub> = V <sub>IL</sub> , V <sub>IH</sub>                  |       |      | ±25   | μΑ     |

| POWER SUPPLY                         | חוי ישוי ן                         | vi Di                                                                 |       |      | -20   | _ μ/ \ |

| Positive Supply Voltage              | V+                                 |                                                                       | 4.75  |      | 5.25  | V      |

| SYNC Supply Voltage                  | DV+                                |                                                                       | 4.75  |      | 5.25  | V      |

| Negative Supply Voltage              | V                                  |                                                                       | -4.75 |      | -5.25 | V      |

| Positive Supply Current              | l+                                 |                                                                       | 7.73  | 35   | 45    | mA     |

| SYNC Supply Current                  |                                    |                                                                       |       | 1    | 2     | mA     |

| Negative Supply Current              | I <sub>DV+</sub>                   |                                                                       |       | 45   | 55    | mA     |

| rvegative supply Current             | '                                  |                                                                       |       | 40   | აა    | IIIA   |

**Note 1:** Guaranteed by duty-cycle test on square wave.

Note 2: V<sub>REF</sub> is independent of V-.

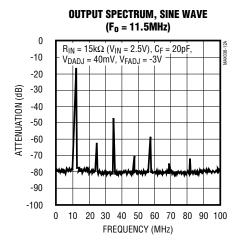

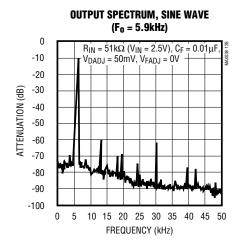

### Typical Operating Characteristics

(Circuit of Figure 1, V+ = DV+ = 5V, V- = -5V,  $V_{DADJ} = V_{FADJ} = V_{PDI} = V_{PDO} = 0V$ ,  $R_L = 1k\Omega/$ ,  $C_L = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

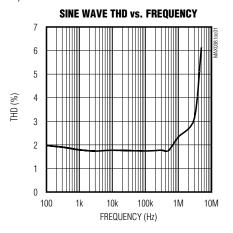

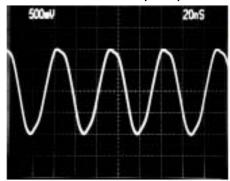

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V+ = DV+ = 5V, V- = -5V,  $V_{DADJ} = V_{FADJ} = V_{PDI} = V_{PDO} = 0V$ ,  $R_L = 1k\Omega$ /,  $C_L = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

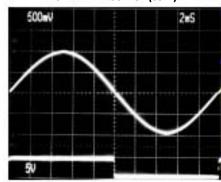

#### **SINE-WAVE OUTPUT (20MHz)**

$\begin{array}{l} I_{IN} = 400 \mu A \\ C_F = 20 p F \end{array}$

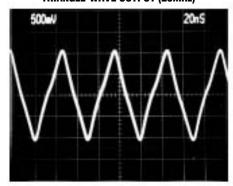

#### TRIANGLE-WAVE OUTPUT (20MHz)

$\begin{array}{l} I_{IN} = 400 \mu A \\ C_F = 20 p F \end{array}$

#### SINE-WAVE OUTPUT (50Hz)

TOP: OUTPUT 50Hz =  $F_0$  BOTTOM: SYNC  $I_{IN} = 50 \mu A$   $C_F = 1 \mu F$

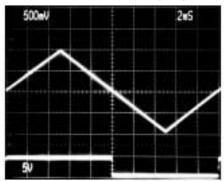

### TRIANGLE-WAVE OUTPUT (50Hz)

TOP: OUTPUT 50Hz =  $F_0$ BOTTOM: SYNC  $I_{IN} = 50\mu A$  $C_F = 1\mu F$

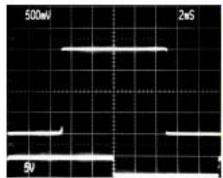

### **SQUARE-WAVE OUTPUT (50Hz)**

TOP: OUTPUT 50Hz =  $F_0$ BOTTOM: SYNC  $I_{IN} = 50\mu A$  $C_F = 1\mu F$

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V+ = DV+ = 5V, V- = -5V,  $V_{DADJ} = V_{FADJ} = V_{PDI} = V_{PDO} = 0V$ ,  $R_L = 1k\Omega/$ ,  $C_L = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

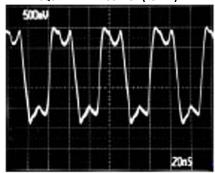

#### **SQUARE-WAVE OUTPUT (20MHz)**

$\begin{array}{l} I_{IN} = 400 \mu A \\ C_F = 20 p F \end{array}$

TOP: OUTPUT BOTTOM: I<sub>IN</sub>

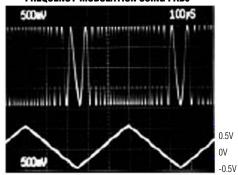

#### FREQUENCY MODULATION USING FADJ

TOP: OUTPUT BOTTOM: FADJ

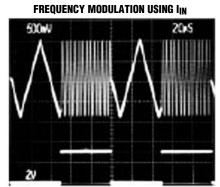

#### FREQUENCY MODULATION USING IIN

TOP: OUTPUT BOTTOM: I<sub>IN</sub>

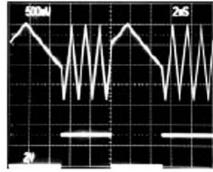

#### PULSE-WIDTH MODULATION USING DADJ

TOP: SQUARE-WAVE OUT, 2V<sub>P-P</sub> BOTTOM: V<sub>DADJ.</sub> -2V to +2.3V

### Typical Operating Characteristics (continued)

(Circuit of Figure 1, V+ = DV+ = 5V, V- = -5V,  $V_{DADJ} = V_{FADJ} = V_{PDI} = V_{PDO} = 0V$ ,  $R_L = 1k\Omega/$ ,  $C_L = 20pF$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| PIN                | NAME | FUNCTION                                                                                                                                                       |  |  |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                  | REF  | 2.50V bandgap voltage reference output                                                                                                                         |  |  |

| 2, 6, 9,<br>11, 18 | GND  | Ground*                                                                                                                                                        |  |  |

| 3                  | A0   | Waveform selection input; TTL/CMOS compatible                                                                                                                  |  |  |

| 4                  | A1   | Waveform selection input; TTL/CMOS compatible                                                                                                                  |  |  |

| 5                  | COSC | External capacitor connection                                                                                                                                  |  |  |

| 7                  | DADJ | Duty-cycle adjust input                                                                                                                                        |  |  |

| 8                  | FADJ | Frequency adjust input                                                                                                                                         |  |  |

| 10                 | IIN  | Current input for frequency control                                                                                                                            |  |  |

| 12                 | PDO  | Phase detector output. Connect to GND if phase detector is not used.                                                                                           |  |  |

| 13                 | PDI  | Phase detector reference clock input. Connect to GND if phase detector is not used.                                                                            |  |  |

| 14                 | SYNC | TTL/CMOS-compatible output, referenced between DGND and DV+. Permits the internal oscillator to be synchronized with an external signal. Leave open if unused. |  |  |

| 15                 | DGND | Digital ground                                                                                                                                                 |  |  |

| 16                 | DV+  | Digital +5V supply input. Can be left open if SYNC is not used.                                                                                                |  |  |

| 17                 | V+   | +5V supply input                                                                                                                                               |  |  |

| 19                 | OUT  | Sine, square, or triangle output                                                                                                                               |  |  |

| 20                 | V-   | -5V supply input                                                                                                                                               |  |  |

<sup>\*</sup>The five GND pins are not internally connected. Connect all five GND pins to a quiet ground close to the device. A ground plane is recommended (see Layout Considerations).

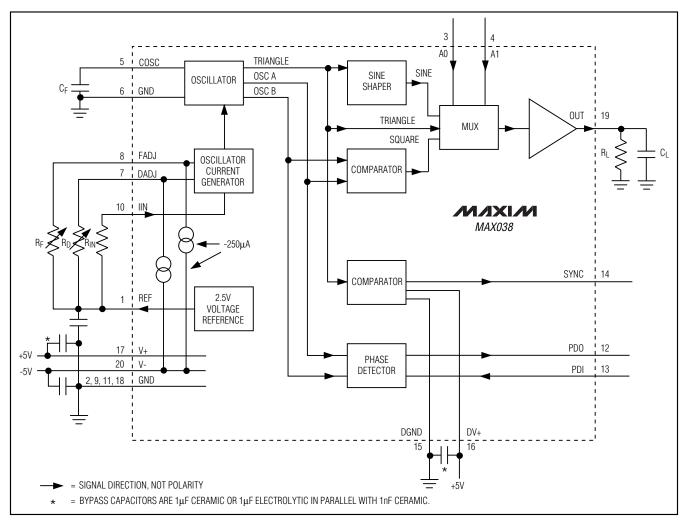

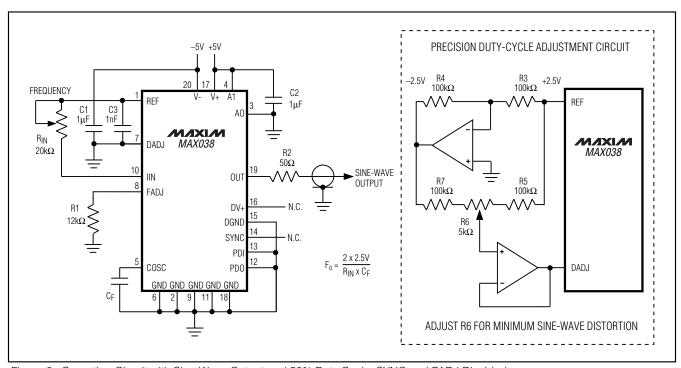

Figure 1. Block Diagram and Basic Operating Circuit

### **Detailed Description**

The MAX038 is a high-frequency function generator that produces low-distortion sine, triangle, sawtooth, or square (pulse) waveforms at frequencies from less than 1Hz to 20MHz or more, using a minimum of external components. Frequency and duty cycle can be independently controlled by programming the current, voltage, or resistance. The desired output waveform is selected under logic control by setting the appropriate code at the A0 and A1 inputs. A SYNC output and phase detector are included to simplify designs requiring tracking to an external signal source.

The MAX038 operates with  $\pm 5V$   $\pm 5\%$  power supplies. The basic oscillator is a relaxation type that operates by alternately charging and discharging a capacitor, C<sub>F</sub>,

with constant currents, simultaneously producing a triangle wave and a square wave (Figure 1). The charging and discharging currents are controlled by the current flowing into IIN, and are modulated by the voltages applied to FADJ and DADJ. The current into IIN can be varied from  $2\mu A$  to  $750\mu A$ , producing more than two decades of frequency for any value of CF. Applying  $\pm 2.4V$  to FADJ changes the nominal frequency (with VFADJ = 0V) by  $\pm 70\%$ ; this procedure can be used for fine control.

Duty cycle (the percentage of time that the output waveform is positive) can be controlled from 10% to 90% by applying  $\pm 2.3V$  to DADJ. This voltage changes the CF charging and discharging current ratio while maintaining nearly constant frequency.

\_\_ /N/1XI/M

A stable 2.5V reference voltage, REF, allows simple determination of IIN, FADJ, or DADJ with fixed resistors, and permits adjustable operation when potentiometers are connected from each of these inputs to REF. FADJ and/or DADJ can be grounded, producing the nominal frequency with a 50% duty cycle.

The output frequency is inversely proportional to capacitor CF. CF values can be selected to produce frequencies above 20MHz.

A sine-shaping circuit converts the oscillator triangle wave into a low-distortion sine wave with constant amplitude. The triangle, square, and sine waves are input to a multiplexer. Two address lines, A0 and A1, control which of the three waveforms is selected. The output amplifier produces a constant 2VP-P amplitude (±1V), regardless of wave shape or frequency.

The triangle wave is also sent to a comparator that produces a high-speed square-wave SYNC waveform that can be used to synchronize other oscillators. The SYNC circuit has separate power-supply leads and can be disabled.

Two other phase-quadrature square waves are generated in the basic oscillator and sent to one side of an "exclusive-OR" phase detector. The other side of the phase-detector input (PDI) can be connected to an external oscillator. The phase-detector output (PDO) is a current source that can be connected directly to FADJ to synchronize the MAX038 with the external oscillator.

#### **Waveform Selection**

The MAX038 can produce either sine, square, or triangle waveforms. The TTL/CMOS-logic address pins (A0 and A1) set the waveform, as shown below:

| A0 | A1 | WAVEFORM      |  |

|----|----|---------------|--|

| Х  | 1  | Sine wave     |  |

| 0  | 0  | Square wave   |  |

| 1  | 0  | Triangle wave |  |

X = Don't care.

Waveform switching can be done at any time, without regard to the phase of the output. Switching occurs within 0.3µs, but there may be a small transient in the output waveform that lasts 0.5µs.

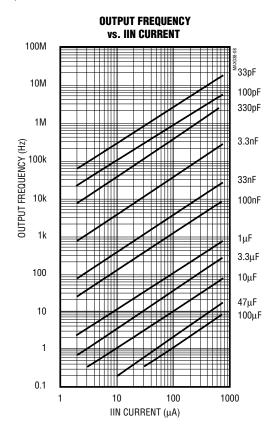

## Waveform Timing Output Frequency

The output frequency is determined by the current injected into the IIN pin, the COSC capacitance (to ground), and the voltage on the FADJ pin. When

VFADJ = 0V, the fundamental output frequency (Fo) is given by the formula:

Fo (MHz) =

$$I_{IN}$$

( $\mu$ A) ÷  $C_F$  ( $pF$ ) [1]

The period (to) is:

to (

$$\mu$$

s) = C<sub>F</sub> ( $p$ F)  $\div$  I<sub>IN</sub> ( $\mu$ A) [2]

where

$I_{IN}=$  current injected into IIN (between  $2\mu A$  and  $750\mu A)$

$C_F$  = capacitance connected to COSC and GND (20pF to >100µF).

For example:

$$0.5MHz = 100\mu A \div 200pF$$

and

$$2\mu s = 200pF \div 100\mu A$$

Optimum performance is achieved with IIN between  $10\mu A$  and  $400\mu A$ , although linearity is good with IIN between  $2\mu A$  and  $750\mu A$ . Current levels outside of this range are not recommended. For fixed-frequency operation, set IIN to approximately  $100\mu A$  and select a suitable capacitor value. This current produces the lowest temperature coefficient, and produces the lowest frequency shift when varying the duty cycle.

The capacitance can range from 20pF to more than  $100\mu F$ , but stray circuit capacitance must be minimized by using short traces. Surround the COSC pin and the trace leading to it with a ground plane to minimize coupling of extraneous signals to this node. Oscillation above 20MHz is possible, but waveform distortion increases under these conditions. The low frequency limit is set by the leakage of the COSC capacitor and by the required accuracy of the output frequency. Lowest frequency operation with good accuracy is usually achieved with  $10\mu F$  or greater non-polarized capacitors.

An internal closed-loop amplifier forces IIN to virtual ground, with an input offset voltage less than  $\pm 2$ mV. IIN may be driven with either a current source (IIN), or a voltage (V<sub>IN</sub>) in series with a resistor (R<sub>IN</sub>). (A resistor between REF and IIN provides a convenient method of generating I<sub>IN</sub>: I<sub>IN</sub> = V<sub>REF</sub>/R<sub>IN</sub>.) When using a voltage in series with a resistor, the formula for the oscillator frequency is:

Fo (MHz) = VIN

$$\div$$

[R<sub>IN</sub> x C<sub>F</sub> (pF)] [3]

and:

to (

$$\mu$$

s) = C<sub>F</sub>( $\rho$ F) x R<sub>IN</sub> ÷ V<sub>IN</sub> [4]

When the MAX038's frequency is controlled by a voltage source (VIN) in series with a fixed resistor (RIN), the output frequency is a direct function of VIN as shown in the above equations. Varying VIN modulates the oscillator frequency. For example, using a  $10k\Omega$  resistor for RIN and sweeping VIN from 20mV to 7.5V produces large frequency deviations (up to 375:1). Select RIN so that IIN stays within the 2µA to 750µA range. The bandwidth of the IIN control amplifier, which limits the modulating signal's highest frequency, is typically 2MHz.

I<sub>IN</sub> can be used as a summing point to add or subtract currents from several sources. This allows the output frequency to be a function of the sum of several variables. As V<sub>IN</sub> approaches 0V, the I<sub>IN</sub> error increases due to the offset voltage of I<sub>IN</sub>.

Output frequency will be offset 1% from its final value for 10 seconds after power-up.

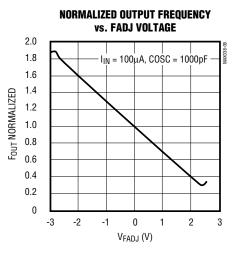

FADJ Input The output frequency can be modulated by FADJ, which is intended principally for fine frequency control, usually inside phase-locked loops. Once the funda-mental, or center frequency ( $F_0$ ) is set by  $I_{IN}$ , it may be changed further by setting FADJ to a voltage other than 0V. This voltage can vary from -2.4V to +2.4V, causing the output frequency to vary from 1.7 to 0.30 times the value when FADJ is 0V ( $F_0$  ±70%). Voltages beyond ±2.4V can cause instability or cause the frequency change to reverse slope.

The voltage on FADJ required to cause the output to deviate from Fo by Dx (expressed in %) is given by the formula:

$$V_{FADJ} = -0.0343 \times D_X$$

[5]

where  $V_{FADJ}$ , the voltage on FADJ, is between -2.4V and +2.4V.

Note: While  $I_{IN}$  is directly proportional to the fundamental, or center frequency (F<sub>0</sub>), V<sub>FADJ</sub> is linearly related to % deviation from F<sub>0</sub>. V<sub>FADJ</sub> goes to either side of 0V, corresponding to plus and minus deviation.

The voltage on FADJ for any frequency is given by the formula:

$$V_{FADJ} = (F_0 - F_X) \div (0.2915 \times F_0)$$

[6]

where:

$F_X$  = output frequency

$F_0$  = frequency when  $V_{FADJ} = 0V$ .

Likewise, for period calculations:

$$V_{FADJ} = 3.43 \times (t_{X} - t_{O}) \div t_{X}$$

[7]

where:

t<sub>X</sub> = output period

$t_0$  = period when  $V_{FADJ} = 0V$ .

Conversely, if VFADJ is known, the frequency is given by:

$$F_X = F_0 \times (1 - [0.2915 \times V_{FADJ}])$$

[8]

and the period (tx) is:

$$t_X = t_O \div (1 - [0.2915 \times V_{FADJ}])$$

[9]

### Programming FADJ

FADJ has a 250 $\mu$ A constant current sink to V- that must be furnished by the voltage source. The source is usually an op-amp output, and the temperature coefficient of the current sink becomes unimportant. For manual adjustment of the deviation, a variable resistor can be used to set VFADJ, but then the 250 $\mu$ A current sink's temperature coefficient becomes significant. Since external resistors cannot match the internal temperature-coefficient curve, using external resistors to program VFADJ is intended only for manual operation, when the operator can correct for any errors. This restriction does not apply when VFADJ is a true voltage source.

A variable resistor, RF, connected between REF (+2.5V) and FADJ provides a convenient means of manually setting the frequency deviation. The resistance value (RF) is:

$$R_F = (V_{REF} - V_{FADJ}) \div 250 \mu A$$

[10]

$V_{REF}$  and  $V_{FADJ}$  are signed numbers, so use correct algebraic convention. For example, if  $V_{FADJ}$  is -2.0V (+58.3% deviation), the formula becomes:

$$R_F = (+2.5V - (-2.0V)) \div 250\mu A$$

=  $(4.5V) \div 250\mu A$

=  $18k\Omega$

### Disabling FADJ

The FADJ circuit adds a small temperature coefficient to the output frequency. For critical open-loop applications, it can be turned off by connecting FADJ to GND (not REF) through a  $12k\Omega$  resistor (R1 in Figure 2). The -250µA current sink at FADJ causes -3V to be developed across this resistor, producing two results. First, the FADJ circuit remains in its linear region, but disconnects itself from the main oscillator, improving temperature stability. Second, the oscillator frequency doubles. If FADJ is turned off in this manner, be sure to correct equations 1-4 and 6-9 above, and 12 and 14 below by doubling  $F_0$  or halving  $t_0$ . Although this method doubles the normal output frequency, it does not double the upper frequency limit. Do not operate FADJ open circuit or with voltages more negative than -3.5V. Doing so may cause transistor saturation inside the IC, leading to unwanted changes in frequency and duty cycle.

Figure 2. Operating Circuit with Sine-Wave Output and 50% Duty Cycle; SYNC and FADJ Disabled

With FADJ disabled, the output frequency can still be changed by modulating I<sub>IN</sub>.

### Swept Frequency Operation

The output frequency can be swept by applying a varying signal to IIN or FADJ. IIN has a wider range, slightly slower response, lower temperature coefficient, and requires a single polarity current source. FADJ may be used when the swept range is less than ±70% of the center frequency, and it is suitable for phase-locked loops and other low-deviation, high-accuracy closed-loop controls. It uses a sweeping voltage symmetrical about ground.

Connecting a resistive network between REF, the voltage source, and FADJ or IIN is a convenient means of offsetting the sweep voltage.

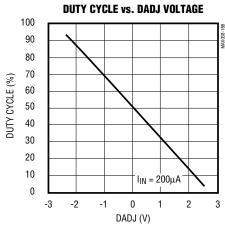

#### Duty Cycle

The voltage on DADJ controls the waveform duty cycle (defined as the percentage of time that the output waveform is positive). Normally,  $V_{DADJ} = 0V$ , and the duty cycle is 50% (Figure 2). Varying this voltage from +2.3V to -2.3V causes the output duty cycle to vary from 15% to 85%, about -15% per volt. Voltages beyond  $\pm 2.3V$  can shift the output frequency and/or cause instability.

DADJ can be used to reduce the sine-wave distortion. The unadjusted duty cycle ( $V_{DADJ} = 0V$ ) is 50%  $\pm 2\%$ ; any deviation from exactly 50% causes even order harmonics to be generated. By applying a small adjustable voltage (typically less than  $\pm 100$ mV) to  $V_{DADJ}$ , exact symmetry can be attained and the distortion can be minimized (see Figure 2).

The voltage on DADJ needed to produce a specific duty cycle is given by the formula:

$$V_{DADJ} = (50\% - dc) \times 0.0575$$

[11]

or:

$$V_{DADJ} = (0.5 - [t_{ON} \div t_{o}]) \times 5.75$$

[12]

where:

V<sub>DADJ</sub> = DADJ voltage (observe the polarity)

dc = duty cycle (in %)

ton = ON (positive) time

$t_0$  = waveform period.

Conversely, if VDADJ is known, the duty cycle and ON time are given by:

$$dc = 50\% - (V_{DADJ} \times 17.4)$$

[13]

$$t_{ON} = to \times (0.5 - [V_{DADJ} \times 0.174])$$

[14]

#### **Programming DADJ**

DADJ is similar to FADJ; it has a 250µA constant current sink to V- that must be furnished by the voltage source. The source is usually an op-amp output, and the temperature coefficient of the current sink becomes unimportant. For manual adjustment of the duty cycle, a variable resistor can be used to set VDADJ, but then the 250µA current sink's temperature coefficient becomes significant. Since external resistors cannot match the internal temperature-coefficient curve, using external resistors to program VDADJ is intended only for manual operation, when the operator can correct for any errors. This restriction does not apply when VDADJ is a true voltage source.

A variable resistor, RD, connected between REF (+2.5V) and DADJ provides a convenient means of manually setting the duty cycle. The resistance value  $(R_D)$  is:

$$RD = (V_{REF} - V_{DADJ}) \div 250\mu A$$

[15]

Note that both V<sub>REF</sub> and V<sub>DADJ</sub> are signed values, so observe correct algebraic convention. For example, if V<sub>DADJ</sub> is -1.5V (23% duty cycle), the formula becomes:

R<sub>D</sub> =

$$(+2.5V - (-1.5V)) \div 250\mu$$

A

=  $(4.0V) \div 250\mu$ A =  $16k$ Ω

Varying the duty cycle in the range 15% to 85% has minimal effect on the output frequency—typically less than 2% when  $25\mu A < I_{IN} < 250\mu A$ . The DADJ circuit is wideband, and can be modulated at up to 2MHz (see photos, *Typical Operating Characteristics*).

#### Output

The output amplitude is fixed at 2Vp-p, symmetrical around ground, for all output waveforms. OUT has an output resistance of under 0.1 $\Omega$ , and can drive  $\pm 20$ mA with up to a 50pF load. Isolate higher output capacitance from OUT with a resistor (typically  $50\Omega$ ) or buffer amplifier.

#### Reference Voltage

REF is a stable 2.50V bandgap voltage reference capable of sourcing 4mA or sinking  $100\mu A$ . It is principally used to furnish a stable current to IIN or to bias DADJ and FADJ. It can also be used for other applications external to the MAX038. Bypass REF with 100nF to minimize noise.

#### **Selecting Resistors and Capacitors**

The MAX038 produces a stable output frequency over time and temperature, but the capacitor and resistors that determine frequency can degrade performance if they are not carefully chosen. Resistors should be metal film, 1% or better. Capacitors should be chosen

for low temperature coefficient over the whole temperature range. NPO ceramics are usually satisfactory.

The voltage on COSC is a triangle wave that varies between 0V and -1V. Polarized capacitors are generally not recommended (because of their outrageous temperature dependence and leakage currents), but if they are used, the negative terminal should be connected to COSC and the positive terminal to GND. Large-value capacitors, necessary for very low frequencies, should be chosen with care, since potentially large leakage currents and high dielectric absorption can interfere with the orderly charge and discharge of CF. If possible, for a given frequency, use lower IIN currents to reduce the size of the capacitor.

#### **SYNC Output**

SYNC is a TTL/CMOS-compatible output that can be used to synchronize external circuits. The SYNC output is a square wave whose rising edge coincides with the output rising sine or triangle wave as it crosses through 0V. When the square wave is selected, the rising edge of SYNC occurs in the middle of the positive half of the output square wave, effectively 90; ahead of the output. The SYNC duty cycle is fixed at 50% and is independent of the DADJ control.

Because SYNC is a very-high-speed TTL output, the high-speed transient currents in DGND and DV+ can radiate energy into the output circuit, causing a narrow spike in the output waveform. (This spike is difficult to see with oscilloscopes having less than 100MHz bandwidth). The inductance and capacitance of IC sockets tend to amplify this effect, so sockets are not recommended when SYNC is on. SYNC is powered from separate ground and supply pins (DGND and DV+), and it can be turned off by making DV+ open circuit. If synchronization of external circuits is not used, turning off SYNC by DV+ opening eliminates the spike.

#### Phase Detectors

#### Internal Phase Detector

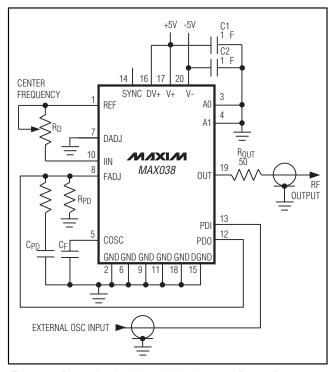

The MAX038 contains a TTL/CMOS phase detector that can be used in a phase-locked loop (PLL) to synchronize its output to an external signal (Figure 3). The external source is connected to the phase-detector input (PDI) and the phase-detector output is taken from PDO. PDO is the output of an exclusive-OR gate, and produces a rectangular current waveform at the MAX038 output frequency, even with PDI grounded. PDO is normally connected to FADJ and a resistor, RPD, and a capacitor CPD, to GND. RPD sets the gain of the phase detector, while the capacitor attenuates high-frequency components and forms a pole in the phase-locked loop filter.

Figure 3. Phase-Locked Loop Using Internal Phase Detector

PDO is a rectangular current-pulse train, alternating between  $0\mu A$  and  $500\mu A$ . It has a 50% duty cycle when the MAX038 output and PDI are in phase-quadrature (90; out of phase). The duty cycle approaches 100% as the phase difference approaches 180° and conversely, approaches 0% as the phase difference approaches 0°. The gain of the phase detector (KD) can be expressed as:

$$K_D = 0.318 \times R_{PD}$$

(volts/radian) [16]

where RpD = phase-detector gain-setting resistor.

When the loop is in lock, the input signals to the phase detector are in approximate phase quadrature, the duty cycle is 50%, and the average current at PDO is 250µA (the current sink of FADJ). This current is divided between FADJ and RPD; 250µA always goes into FADJ and any difference current is developed across RPD, creating VFADJ (both polarities). For example, as the phase difference increases, PDO duty cycle increases, the average current increases, and the voltage on RPD (and VFADJ) becomes more positive. This in turn decreases the oscillator frequency, reducing the phase difference, thus maintaining phase lock. The higher RPD is, the greater VFADJ is for a given phase difference; in other words, the greater the loop gain, the less the capture range. The current from PDO must also

charge C<sub>PD</sub>, so the rate at which V<sub>FADJ</sub> changes (the loop bandwidth) is inversely proportional to C<sub>PD</sub>.

The phase error (deviation from phase quadrature) depends on the open-loop gain of the PLL and the initial frequency deviation of the oscillator from the external signal source. The oscillator conversion gain  $(K_0)$  is:

$$K_{O} = \Delta \omega_{O} \div \Delta V_{FADJ}$$

[17]

which, from equation [6] is:

$$K_O = 0.2915 \times \omega_O \text{ (radians/sec)}$$

[18]

The loop gain of the PLL system (K<sub>V</sub>) is:

$$K_V = K_D \times K_O$$

[19]

where:

KD = detector gain

Ko = oscillator gain.

With a loop filter having a response F(s), the open-loop transfer function, T(s), is:

$$T(s) = K_D \times K_O \times F(s) \div s \qquad [20]$$

Using linear feedback analysis techniques, the closed-loop transfer characteristic, H(s), can be related to the open-loop transfer function as follows:

$$H(s) = T(s) \div [1 + T(s)]$$

[21]

The transient performance and the frequency response of the PLL depends on the choice of the filter characteristic, F(s).

When the MAX038 internal phase detector is not used, PDI and PDO should be connected to GND.

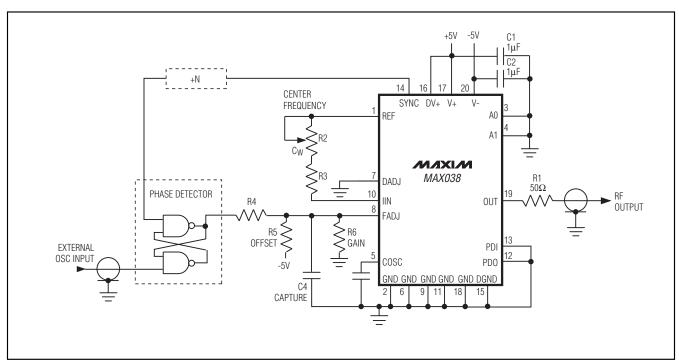

#### External Phase Detectors

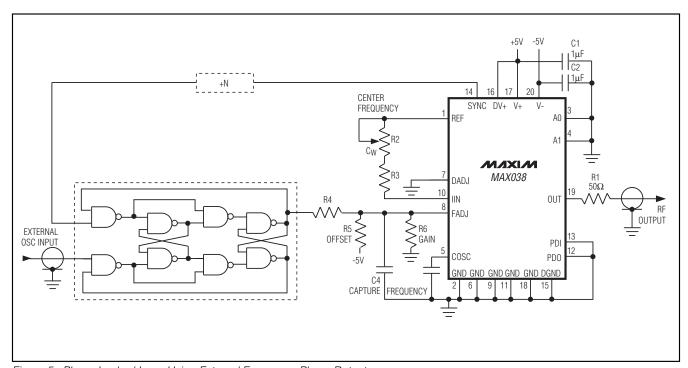

External phase detectors may be used instead of the internal phase detector. The external phase detector shown in Figure 4 duplicates the action of the MAX038's internal phase detector, but the optional ÷N circuit can be placed between the SYNC output and the phase detector in applications requiring synchronizing to an exact multiple of the external oscillator. The resistor network consisting of R4, R5, and R6 sets the sync range, while capacitor C4 sets the capture range. Note that this type of phase detector (with or without the ÷N circuit) locks onto harmonics of the external oscillator as well as the fundamental. With no external oscillator input, this circuit can be unpredictable, depending on the state of the external input DC level.

Figure 4 shows a frequency phase detector that locks onto only the fundamental of the external oscillator. With no external oscillator input, the output of the frequency phase detector is a positive DC voltage, and the oscillations are at the lowest frequency as set by R4. R5. and R6.

Figure 4. Phase-Locked Loop Using External Phase Detector

Figure 5. Phase-Locked Loop Using External Frequency Phase Detector

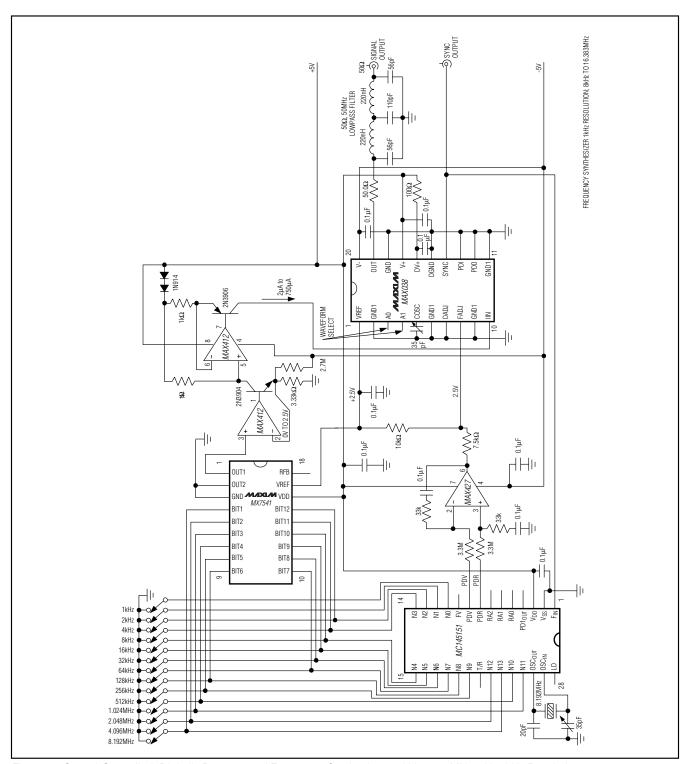

Figure 6. Crystal-Controlled, Digitally Programmed Frequency Synthesizer—8kHz to 16MHz with 1kHz Resolution

### **Layout Considerations**

Realizing the full performance of the MAX038 requires careful attention to power-supply bypassing and board layout. Use a low-impedance ground plane, and connect all five GND pins directly to it. Bypass V+ and V-directly to the ground plane with 1µF ceramic capacitors or 1µF tantalum capacitors in parallel with 1nF ceramics. Keep capacitor leads short (especially with the 1nF ceramics) to minimize series inductance.

If SYNC is used, DV+ must be connected to V+, DGND must be connected to the ground plane, and a second 1nF ceramic should be connected as close as possible between DV+ and DGND (pins 16 and 15). It is not necessary to use a separate supply or run separate traces to DV+. If SYNC is disabled, leave DV+ open. Do not open DGND.

Minimize the trace area around COSC (and the ground plane area under COSC) to reduce parasitic capacitance, and surround this trace with ground to prevent coupling with other signals. Take similar precautions with DADJ, FADJ, and IIN. Place CF so its connection to the ground plane is close to pin 6 (GND).

# Applications Information Frequency Synthesizer

Figure 6 shows a frequency synthesizer that produces accurate and stable sine, square, or triangle waves with a frequency range of 8kHz to 16.383MHz in 1kHz increments. A Motorola MC145151 provides the crystal-controlled oscillator, the ÷N circuit, and a high-speed phase detector. The manual switches set the output frequency; opening any switch increases the output frequency. Each switch controls both the ÷N output and an MX7541 12-bit DAC, whose output is converted to a current by using both halves of the MAX412 op amp. This current goes to the MAX038 IIN pin, setting its coarse frequency over a very wide range.

Fine frequency control (and phase lock) is achieved from the MC145151 phase detector through the differential amplifier and lowpass filter, U5. The phase detec-

### \_Package Information

For the latest package outline information, go to www.maxim-ic.com/packages.

### \_Revision History

Pages changed at Rev 7: 13, 16

tor compares the ÷N output with the MAX038 SYNC output and sends differential phase information to U5. U5's single-ended output is summed with an offset into the FADJ input. (Using the DAC and the IIN pin for coarse frequency control allows the FADJ pin to have very fine control with reasonably fast response to switch changes.)

A 50MHz,  $50\Omega$  lowpass filter in the output allows passage of 16MHz square waves and triangle waves with reasonable fidelity, while stopping high-frequency noise generated by the  $\div N$  circuit.

### Chip Topography

TRANSISTOR COUNT: 855

SUBSTRATE CONNECTED TO GND

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.